- 1 2024.04.10 Dorazily 1502 a programátor

- 2 2024.02.10 Robodoupě

- 3 2024.02.06 Part 1+2 again

- 4 2024.02.05 ATF1504AS - modul a part 2

- 5 2024.02.03 part 1

- 6 2024.01.28 ATF1504AS

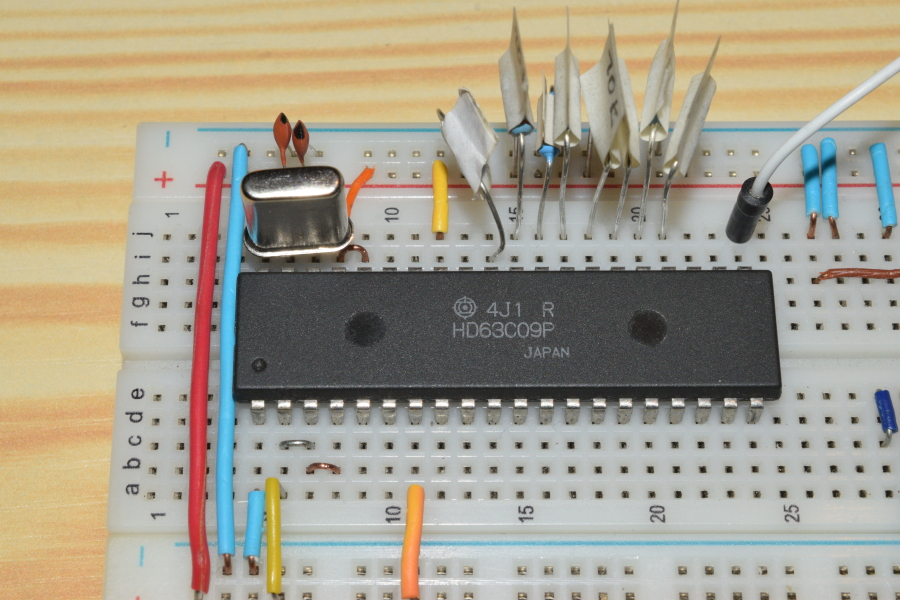

- 7 2024.01.27 Test HD6309

- 8 2024.01.25 Kicad

- 9 2024.01.22

- 10 2024.01.20 I2C + SPI konektor

- 11 2024.01.18 Krystaly 14.7456 MHz a 16 MHz, RAM místo ROM, $8000 .. 8K bank?

- 12 2024.01.16 Ruby comp, BBC Micro out, shared RAM w. ATMEGA

- 13 2024.01.14 Sběrnice, desky, ...

- 14 2024.01.13 openScad

- 15 2024.01.10 Akvizice

- 16 2024.01.03 Nový Blog

- 17 2024.01.02 Nový Rok

- 18 Postřehy (jak to dělají jinde, co mě napadlo)

- 19 Parts

- 20 ToDo

- 21 Done

1 2024.04.10 Dorazily 1502 a programátor

Takže to zkouším znova - device name je asi f1502ispplcc44 podle .wine/drive_c/Wincupl/Shared/Atmel.cat heslo pro AVRISP 60008009

2 2024.02.10 Robodoupě

- Na chlubírnu jsem přinesl ukázku jak Arduino UNO přez kompozitní signál a RCA ovládá monitor - postavil jsem to podle https://www.youtube.com/watch?v=Th18tLP86WQ jenom jsem tam dal jeden odpor menší (500 Ω místo 1 kΩ na TX), protože to na mojem monitorku svítilo místy špatně. Snížením odporu na polovinu se jas zvedl a všechny body byly dost vysvícené :)

3 2024.02.06 Part 1+2 again

Příprava

su -

uname -a

Linux cobra-mk3 6.1.19-gentoo #1 SMP PREEMPT_DYNAMIC Sun Aug 27 01:29:22 CEST 2023 x86_64 AMD Ryzen 9 3900X 12-Core Processor AuthenticAMD GNU/Linux

echo "dev-embedded/openocd ~amd64" >>/etc/portage/package.accept_keywords/openocd

gemerge -avq openocd

* Last emerge --sync was Sun Mar 19 05:40:02 2023.

[ebuild N ] acct-group/plugdev-0-r1

[ebuild N ] dev-lang/jimtcl-0.81 USE="-doc -static-libs"

[ebuild N ] dev-embedded/libjaylink-0.3.1

[ebuild N ] dev-embedded/libftdi-1.5-r4 USE="-cxx -doc -examples -python -test -tools" PYTHON_SINGLE_TARGET="python3_10 -python3_9"

[ebuild N ] dev-embedded/openocd-0.12.0 USE="cmsis-dap ftdi jlink usb -capstone -dummy -parport -verbose-io"

Would you like to merge these packages? [Yes/No] y

...

useradd -m -g users -G plugdev SomeUserName

passwd SomeUserName

cat >/etc/udev/rules.d/99-usbBlaster.rules

# Intel FPGA Download Cable

SUBSYSTEM=="usb", ENV{DEVTYPE}=="usb_device", ATTR{idVendor}=="09fb", ATTR{idProduct}=="6001", MODE="0666", SYMLINK+="UsbBlaster"

SUBSYSTEM=="usb", ENV{DEVTYPE}=="usb_device", ATTR{idVendor}=="09fb", ATTR{idProduct}=="6002", MODE="0666", SYMLINK+="UsbBlaster"

SUBSYSTEM=="usb", ENV{DEVTYPE}=="usb_device", ATTR{idVendor}=="09fb", ATTR{idProduct}=="6003", MODE="0666", SYMLINK+="UsbBlaster"

# Intel FPGA Download Cable II

SUBSYSTEM=="usb", ENV{DEVTYPE}=="usb_device", ATTR{idVendor}=="09fb", ATTR{idProduct}=="6010", MODE="0666", SYMLINK+="UsbBlaster"

SUBSYSTEM=="usb", ENV{DEVTYPE}=="usb_device", ATTR{idVendor}=="09fb", ATTR{idProduct}=="6810", MODE="0666", SYMLINK+="UsbBlaster"

exit

Provedení

su - SomeUserName

mkdir ~/Downloads

cd ~/Downloads/

# obtain or create pld example XorTest.pld

# now the programs ...

# **Part 1**

WINEARCH=win32 WINEPREFIX=~/.wine wine wineboot

WINEARCH=win32 WINEPREFIX=~/.wine winetricks mfc42

# firefox https://www.microchip.com/en-us/search?searchQuery=awincupl&category=ALL&fq=start%3D0%26rows%3D10 select avincupl, download it, or wget the link

wget https://ww1.microchip.com/downloads/en/DeviceDoc/awincupl.exe.zip

unzip -x awincupl.exe.zip

WINEARCH=win32 WINEPREFIX=~/.wine wine ~/Downloads/awincupl.exe

# firefox https://sourceforge.net/projects/cupl-ide/ click download, or wget it (linux version and give it sane name)

wget https://sourceforge.net/projects/cupl-ide/files/3.x.x/latest/CUPLIDE-linux.gtk.x86_64.tar.gz/download -O CUPLIDE-linux.gtk.x86_64.tar.gz

tar -xzf CUPLIDE-linux.gtk.x86_64.tar.gz

~/Downloads/CUPLIDE

# File -> Open File ... -> select Downloads/XorTest.pld, Ctrl-A (select all), Ctrl-C (copy it), Ctrl-W (close it)

# File -> New -> Cupl Project (give it name), Ctrl-A (select all), Ctrl-V (replace it with the Downloads/XorTest.pld content), Ctrl-S (save it), Build -> JEDEC Generator

# File -> Exit, now we have JEDEC file in ~/CUPLworkspace/XorTest/output/XorTest.jed and ASCII chip picture in ~/CUPLworkspace/XorTest/output/XorTest.fit

# firefox https://www.microchip.com/en-us/search?searchQuery=ProChip&category=ALL&fq=start%3D0%26rows%3D10 select Prochip5, download it, or wget the link

# **Part 2**

wget https://ww1.microchip.com/downloads/aemDocuments/documents/OTH/ProductDocuments/SoftwareLibraries/Firmware/ProChip5.zip

unzip -x ProChip5.zip

WINEARCH=win32 WINEPREFIX=~/.wine wine ~/Downloads/ProChip5_setup.exe

# install all, extract FTD CDM Drivers

cp ~/.wine/drive_c/users/*/Temp/FTDI-Driver/i386/ftd2xx.{lib,dll} ~/.wine/drive_c/ATMEL_PLS_Tools/ATMISP/

WINEARCH=win32 WINEPREFIX=~/.wine wine ~/.wine/drive_c/ATMEL_PLS_Tools/ATMISP/ATMISP.exe

# Edit -> Add device , select ATF1504AS, program/verify, file ~/CUPLworkspace/XorTest/output/XorTest.jed, OK, check Write SVF file, select the SVF file. Run, Exit and we have ~/CUPLworkspace/XorTest/output/XorTest.svf

# **Part 3** = modul

# **Part 4** - Blaster V1 process

ls -al /usr/share/openocd/scripts/interface/altera-usb-blaster.cfg

-rw-r--r-- 1 root root 298 2024-02-06 22:45 /usr/share/openocd/scripts/interface/altera-usb-blaster.cfg

ls -al /dev/UsbBlaster

lrwxrwxrwx 1 root root 15 2024-02-06 22:59 /dev/UsbBlaster -> bus/usb/005/058

openocd -f /usr/share/openocd/scripts/interface/altera-usb-blaster.cfg -c "adapter speed 400" -c "jtag newtap ATF1504AS tap -irlen 3 -expected-id 0x0150403f" -c init -c "sleep 200" -c shutdown

Part 3 = modul

Part 4 ...

- nainstalováno mám, UsbBlaster se hlásí, dokonce i něco vidí, ale ne to, co by měl. Myslím si, že po lince leze nějaký bordel, zkusím tam dát ty kondíky

gemerge = emerge --jobs=25 --load-average=25 "$@"

Programování v CUPL https://class.ece.uw.edu/475/peckol/doc/cupl.html

cupl přez skript https://github.com/adrienkohlbecker/cupl.bat

4 2024.02.05 ATF1504AS - modul a part 2

Tak jsem doletoval poslední drátky v testovacím modul pro ATF1504AS a všechno několikrát proměřil a po připojení na napájení to asi neshořelo. Teď to ještě naprogramovat a otestovat a pak se uvidí

- mám JEDEC, nejde mi nainstalovat ATMISP, ... zkusím stáhnout z mikrochipu něco nového ... vyhledám ProChip, najde to ProChip5

rm -r -f ~/.wine

WINEARCH=win32 WINEPREFIX=~/.wine wine wineboot

WINEARCH=win32 WINEPREFIX=~/.wine winetricks mfc42

WINEARCH=win32 WINEPREFIX=~/.wine winetricks

WINEARCH=win32 WINEPREFIX=~/.wine wine ~/Downloads/ProChip5_setup.exe

WINEARCH=win32 WINEPREFIX=~/.wine wine ~/.wine/drive_c/ATMEL_PLS_Tools/ATMISP/ATMISP.exe

0084:fixme:hid:handle_IRP_MN_QUERY_ID Unhandled type 00000005

0084:fixme:hid:handle_IRP_MN_QUERY_ID Unhandled type 00000005

0084:fixme:hid:handle_IRP_MN_QUERY_ID Unhandled type 00000005

0084:fixme:hid:handle_IRP_MN_QUERY_ID Unhandled type 00000005

0024:err:module:import_dll Library FTD2XX.dll (which is needed by L"C:\\ATMEL_PLS_Tools\\ATMISP\\ATMISP.exe") not found

0024:err:module:LdrInitializeThunk Importing dlls for L"C:\\ATMEL_PLS_Tools\\ATMISP\\ATMISP.exe" failed, status c0000135

cp ~/.wine/drive_c/users/*/Temp/FTDI-Driver/i386/ftd2xx.{lib,dll} ~/.wine/drive_c/ATMEL_PLS_Tools/ATMISP/

WINEARCH=win32 WINEPREFIX=~/.wine wine ~/.wine/drive_c/ATMEL_PLS_Tools/ATMISP/ATMISP.exe

5 2024.02.03 part 1

- Zkusil jsem stáhnout assembler HXA a funguje, jen v pythonu je potřeba nahradit NOFLAG za 0 a převést všechny soubory na lowercase jména (nebo mu to opravit)

- dala by se tam přidělat 6309, asi, nějak

- ale jako doporučený assembler je tam i cc65 který má C a assembler

- Dal jsem dohromady testovací modul pro ATF1504AS, ale nemám ho zatím jak programovat. Postup podle http://forum.6502.org/viewtopic.php?f=10&t=7920 se zasekne už v prvním kroku, možná protože mám wine 8.0, nikoli 8.0.2 (asi to spíš viselo na těch winetricks a WINEARCH)

zkusím emergnout wine 8.1, jestli to pomůže

různě to padá a nejede

fix podle náhodného webu pod novým uživatelem:

- PLD -> JEDEC

rm -r -f ~/.wine WINEARCH=win32 WINEPREFIX=~/.wine wine wineboot WINEARCH=win32 WINEPREFIX=~/.wine winetricks mfc40 WINEARCH=win32 WINEPREFIX=~/.wine winetricks WINEARCH=win32 WINEPREFIX=~/.wine wine ~/Downloads/awincupl.exe WINEARCH=win32 WINEPREFIX=~/.wine wine ~/.wine/drive_c/Wincupl/WinCupl/Wincupl.exe

to už jede

- tady je cuplIDE, ale je to asi jenom frontend (a vše musí být v "projektech")

- ano, ale průběžně kontroluje syntaxi a má o fous lepší chybové hlášky než ten Wincupl - takže stojí za to ho používat

- a udělal jsem si modul pro XOR 4 input-only pinů (87-90 = xIO61..xIO64) zpropagovaný na všechny ostatní a střídavě negovaný, pro testy...

po určitých úpravách (přeházení pinů) mi jede i https://mansfield-devine.com/speculatrix/2022/06/a-newbies-introduction-to-cupl-and-cplds/ v 1504 se 100 pin pouzdrem

- nicméně mám způsob, jak získat JEDEC, můžu se snažit o další krok (http://forum.6502.org/viewtopic.php?f=10&t=7920 Part 2)

- a možná nejdřív načíst https://whitequark.github.io/prjbureau/index.html kvůli JEDEC -> SVF - tak nic, ty moduly nejdou nijak rozumně stáhnout (možná jen zatím, ale stejně)

6 2024.01.28 ATF1504AS

- objednal jsem si u TME 2x CLPD ATF1504AS-10 TQFP100 doufám, že to zvládnu naprogramovat a připájet. (USB BLASTER, openOCD)

- CPLD, mělo by to zvládnout veškerou glue logiku včetně D latchů a 3state, 2way, 64 I/O (+4 JTAG) na ploše 16x16 mm (0.5mm mezi středy pinů)

7 2024.01.27 Test HD6309

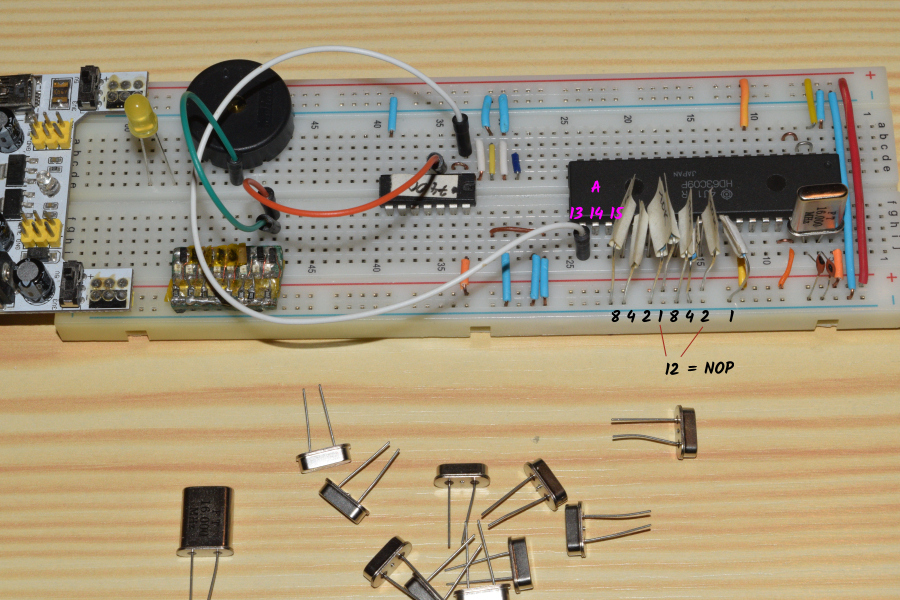

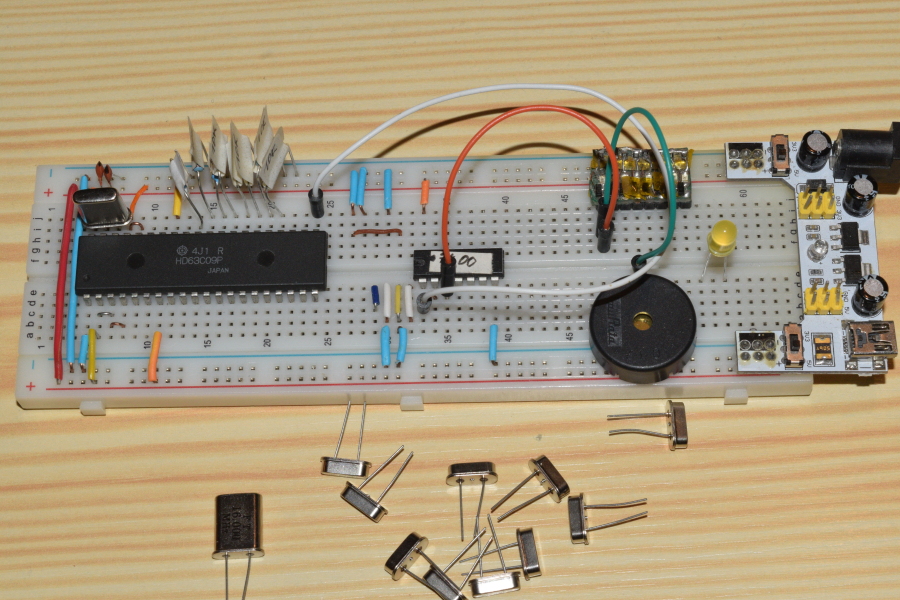

Z aliexpresu přišly tři 8-bitové procesory HD6309P (a opravdu to jsou 6309, nikoli jen 6809 a P, nikoli PE a ačkoli jsou určené "až do 3MHz", tak se rozeběhnou i na 4MHz - viz obrázek z testu) a hrst krystalů 14.7456 MHz (se kterými to běží jen o něco pomaleji než s 16MHz, ale zato na dobře dělitelné frekvenci a tak to má být)

To na obrázku je "NOP generátor", zapojení, kde bez ohledu na adresu má procesor na datových vstupech instrukci No OPeration, takže vesele cykluje i bez spousty přídavných obvodů. Piezo-reproduktorek je přez zesilovaš připojený na adresovou sběrnici, takže je slyšet, jak se tam ty adresy mění (efektivně jde o děličku kmitočtu toho krystalu, kde ho procesor dělí 4, adresy mají 16 bitů takže dělí 65536x a instrukce NOP zabere 2 takty, takže dělí 2x a tím se ty MHz převedou do slyšitelného pásma. Odposloucháváním různých adres se přelaďuje o oktávy. )

8 2024.01.25 Kicad

- Začal jsem kreslit schémata v KiCadu a nějak se to rozrostlo

- Copy-Paste mezi projekty mi nefunguje uspokojivě pro boardy, takže zatím jen umím pastnout schema k existujícímu projektu, syncnout PCB a součástky natahat ručně

- Template se z projektu udělá adresářem meta se souborem info.html a případnou ikonou 64x64 icon.png

- nový projekt z templatu si přejmenuje soubory na ten nový projekt

- Zatím tam mám HD6309 + 2x 32K RAM + Glue logic (4x GAL) + Arduino Mega + 32K RAM na sdílení a pracuju na card logic pro předávání řízení a nějak se to vejde (součástky polochaoticky, autorouter nějak naroutuje)

- ale musím si rozmyslet komunikační protokol, jak si tu RAM předávat

- Arduino Mega by taky mělo emulovat systémovou ROM předvyplněním RAM

- po restartu si musí umět vynutit sběrnici

- card logic - R/W registr pro namapovanou/požadovanou stránku, pořešit chci/nechci

- objednávám z alíka 10xmicroSD(TF) reader s LV125A chipem (4x level shift) (problém s odstíněním non=SPI chování viz Expanduino)

9 2024.01.22

- Specification specifikace, čeho asi tak chci dosáhnout

10 2024.01.20 I2C + SPI konektor

- I2C-6 konektor http://forum.6502.org/viewtopic.php?f=4&t=2155 6 pin (jeden ucvaknutý pro orientaci). U CPU je sameček (piny), zařízení(konektor) má samičku a nasouvá se

. /........................./

//--------------/|......../

//Vcc Clk (cut)/ |......./

/┌────┬────┬────┐ |....../

/.│ 2 │ 4 │ (X)│ /...../

/..├────┼────┼────┤ /...../

/...│ 1 │ 3 │ 5 │/...../

═════╧════╧════╧════╧══════(board edge)

Data Gnd IRQ\

- SP-10 konektor http://forum.6502.org/viewtopic.php?p=48167#p48167

11 2024.01.18 Krystaly 14.7456 MHz a 16 MHz, RAM místo ROM, $8000 .. 8K bank?

- generování hodin plus odkazy na variabilní hodiny (ohulíme to, dokud to snese a pak trochu uberem)

- Pokud bych předvyplnil RAM pomocí ATMEGA, tak nepotřebuju EEPROM a tudíz ji nepotřebuju ani umět vypalovat.

- eventuálně můžu mít EEPROM třeba sériovou pro ATMEGA a zapisovat ji taky odtamtud

- a většinu věcí tahat z SD karty

- Možná by nebyla špatná "půjčovna paměti" pro 8K nad $8000, kde by se na nějaké I/O adrese zažádalo o paměť s daným číslem a odpověď by byla buď "je tam", nebo "teď nelze", nebo "není a nebude"

- každý požadavek by uvolnil aktuální paměť a buď tam namapoval novou, nebo tam namapoval read(FF), write(ignored) emulaci

- paměti by pak byly

- obecné RAM moduly (rozšíření paměti)

- komunikační RAM (buffer, který si předává s ATMEGA)

- tedy i třeba paměťově mapované soubory

- ROM bloky (knihovny, ovladače, ....)

- pseudo ROM bloky (RAM načtená z SD souboru)

- otestoval jsem krystaly 14.7456 MHz a 16 MHz na NOP generátoru a 6309 s nima bez problému běhá na breadboardu

- otestoval jsem taky issue-3 zapojení oscilátoru (74HC04 + 14.7456 MHz krystal + 1 MΩ paralelně a dva kondíky k zemi) a taky to chodí

- I/O ICs 6522 VIA + 6551 ACIA - spousta detailů

13 2024.01.14 Sběrnice, desky, ...

- Úvahy o sběrnici, kde mají být adresy, kde data, kde I/O a kde další signály

- I/O vyhodnotit HW na CPU desce jako prioritní (a nepřemapovávané)

- (1-2) horní ROM mít s defaultem pro ROM (nebo selektovatelně default/poslední)

- možná použít pro pamatování EEPROM místo RAM 8x8?

- spíš ne, protože stejně první starost systému by měla být namapovat si někam RAM pro zásobník a buffery pro I/O a když už to dělá, tak si může snadno namapovat i ten zbytek správně, a ne jen odhadem

- potřebuju mít BOOT ROM namapovanou by default, jakmile se jednou přemapuje, tak je to až do restartu jedno

- takže nejspíš A/B -> Y a RS s defaultem přez pull-up/down

- všechny DIP paměti mají data převážně vpravo dole (a trochu vlevo dole), adresy vlevo nahoře (a trochu chaoticky vpravo nahoře) - ale u RAM můžu mezi sebou libovolně přeházet linky, u EPROM sice taky, ale pak se to zkomplikuje všude jinde, takže raději ne.

- UT62.256 32Kx8 SRAM má data vpravo uprostřed, adresy převážně chaoticky vlevo (ale, jak bylo řečeno, můžu to přečíslovat)

- všechny PIA/VIA/ACIA mají data vpravo uprostřed, D0 nahoře (na tom záleží) a výstupy vlevo

- 6309 má data vpravo uprostřed, D0 nahoře a adresy převážně vlevo (ale ty se budou překládat)

- možná dát sběrnici teda vpravo, data doprostřed, adresy nahoru a I/O dolů?

- na sběrnici půjdou data automaticky přez průchodku 74HC245, jak u desek, tak u CPU

- na desce bude PAL pro vnitřní dekódování adres

- adresa 0000 read bude průchodka 74HC245 s nasvitchovanou adresou

- I/O desky:

- 0000 read bude průchodka 74HC245 s nasvitchovanou adresou

- 0001 read bude výstup 8 RS

- 0000 write reset bits pro 8 RS

- 0001 write set bits pro 8 RS

- 001x R/W ACIA

- 01xx R/W PIA

- Expanduino:

- 0000 read bude průchodka 74HC245 s nasvitchovanou adresou

- 01xx R/W Expanduino 1+3 kanály

- CPU:

- 6309 CPU (+6309 E variant?)

- 16MHz krystal

- 7.3728 MHz krystal pro ACIA system wide - asi by šlo zapojit podle kilo issue3 schema pro 6309E

- glue logika pro I/O[0..7]

- Memory card:

- simple menory:

- A[0..15]+E+R/W -> 74HC00 + RAM + ROM podle OMEN kilo

14 2024.01.13 openScad

- Z Alíka objednávám 10* UT62256C-70LL - 32kB SRAM (á 10.35Kč) - nebudu pracně drátovat sloty 8x8, prsknu tam 32.000x8 a půjde to taky a levně :)

- Paměť rozhodím po 8kB, jedna 32kB RAM bude dole, druhá nad ní pro zrcadlení ROM a pod nepoužitýma devicema - tam si systém může cpát buffery do 7.x kB a přepínání ROM nějak vymyslím a druhý slot se po částech bude mapovat do 8000+8kB

- Z Alíka objednávám 40 M3 16mm spacerů - 10 pater hned tak nedám :)

Nainstaloval jsem openScad (Dokumentace) a upravil si podstavu pro Comp24

Click to expand/collapse code

$fn=200;

include <defaults.scad>;

use <M3.scad>;

use <Nut.scad>;

card=[100+1,100+1,2];

holes=[90,90];

base=[100+4,100+4,6];

wing=60;

radius=2;

difference() {

minkowski(){

cube(base,center=true);

cylinder(r=radius,h=1);

}

for(i=[-1,1]) for(j=[-1,1]) {

translate([i*holes.x/2, j*holes.y/2, -0.5])

NutM3( h=2.5, inset=1);

translate([i*holes.x/2, j*holes.y/2, 10])

BoltM3(l=15, inset=1);

}

translate([0,0,3.1]) {

cube(card, center=true);

cube([wing,base.y+2*radius+1,2],center=true);

cube([base.x+2*radius+1,wing,2],center=true);

}

translate([-30, -base.y/2-1.5,-2.5])

rotate(90,[1,0,0])

linear_extrude(3)

text("Comp24 - Gilhad 2024",size=4, font = "Liberation Sans:style=Bold Italic");

translate([-base.x/2-1.5,28,-2.5])

rotate(90,[1,0,0])

rotate(90,[0,-1,0])

linear_extrude(3)

text("v.0.0.1 date 2024.01.12",size=4, font = "Liberation Sans:style=Bold Italic");

}

- Bevel Gear ozubená kola a kruhy

- rotacniZuby :

Click to expand/collapse rotacniZuby

module rotacniZuby(n=24,d1=10,d2=15,h=2){

difference(){}

color("red")

rotate_extrude()

translate([d1, 0])

square([d2-d1,h]);

color("blue")

translate([0,0,0])

for(i=[0:n-1])

rotate([0,0,i*360/n])

translate([d1,0,0])

rotate([45,0,0])

cube([d2-d1,h,h]);

{}

}

rotacniZuby();

15 2024.01.10 Akvizice

- Z Alíka dorazily zahnuté 40 pin lišty (pro I/O na hranách desek)

- Z Alíka dorazily MC68B50 - ACIA - pro sériovou komunikaci - otestoval jsem je a asi chodí :)

- 2024.01.11 Sběrnice - 2x32 pin header, dlouhé nohy - Výška patra 17mm, z toho 1.5mm tloušťka desky - potřebuju M3 16mm spacery

- Čtu https://wilsonminesco.com/ a jiné věci okolo http://6502.org/, původně kvůli stránkování, ale je tu toho zajímavého výrazně víc

- 8-bit Identity comparators - snadné dekódování adresy

- 2->4 výběr adres, různá logika

- Priority Encoder

- Použití paralelních portů 6522 jako výběr adresy s defaultem po resetu

- víc zemí a napětí na konektoru, rozházené tak, aby to ostatní signály "neměly daleko"

- víc zemních cest na desce spíš než tlusté čáry (0.2 mm stačí na 0.5A)

- Open colector AND může mít dlouhý nárůst napětí - čistit interrupty na začátku ISR, aby to stihly a neudeřily ještě jednou navíc (než se dostatečně nabijou parazitní kapacity)

- video "karta" http://forum.6502.org/viewtopic.php?f=12&t=4482&start=45

16 2024.01.03 Nový Blog

17 2024.01.02 Nový Rok

- Zkouším udělat návrh počítače Comp24 - modeluju v KiCadu obecnou desku a učím se, jak s ním pracovat, zejména Bus-y

18 Postřehy (jak to dělají jinde, co mě napadlo)

- Dekódování adres

- 74HC138 3->8 výběr adres, různá logika

- 74HC139 2x 2->4 výběr adres, různá logika

- 74HC688 - 8-bit Identity comparators - snadné dekódování adresy !!!

- 74HC148 - Priority Encoder - 8->3 první z adres, která sedí

- Použití paralelních portů R6522-VIA / MC6521-PIA jako výběr adresy (možná overkill, ale proč ne?)

- 74HC257 - QUADRUPLE 2-LINE TO 1-LINE DATA SELECTORS/MULTIPLEXERS WITH 3-STATE OUTPUTS - přepíná 4bity: 4A, 4B -> 4Y

- I/O

- generic I2C interface Datapod

- Bit bang?

- Různé obvody a triky

- Testy

- Emulátory a spol

- https://github.com/Rautz/psmame.git obsahuje emulátor hd6309 psmame/src/emu/cpu/hd6309

- Fake6502 CPU emulator core Mike Chambers fake6502.c

- video "karta" http://forum.6502.org/viewtopic.php?f=12&t=4482&start=45

- 74HC377 OCTAL D-TYPE FLIP-FLOPS WITH CLOCK ENABLE - 8xD + Clock+ Enable

- 74HC273 OCTAL D-TYPE FLIP-FLOPS WITH CLEAR - 8xD + Clock + Clear

19 Parts

Click to expand/collapse

- 2024.01.16 Xtal 14.7456 Mhz - pro rychlejší 6309 a ACIA (nebo pro ACIA s děličkou)

- 2024.01.16 74HC74 - D-hradlo s resetem pro Edge RS

- 2024.01.11 Sběrnice - 2x32 pin header, dlouhé nohy

- 2024.01.10 MC68B50 - ACIA - pro sériovou komunikaci

- 2024.01.10 zahnuté 40 pin lišty (pro I/O na hranách desek)

- 2024.01.09 MC68B21CP - PIA - paralelní port

- 2024.01.24 UT62256C - 32K x8 SRAM SMD asi TSOP28

- 2024.01.28 objednal jsem si u TME 2x CLPD ATF1504AS-10 TQFP100 doufám, že to zvládnu naprogramovat a připájet. (USB BLASTER, openOCD)

- CPLD, mělo by to zvládnout veškerou glue logiku včetně D latchů a 3state, 2way, 64 I/O (+4 JTAG) na ploše 16x16 mm (0.5mm mezi středy pinů)

20 ToDo

Click to expand/collapse

- Comp24

- KiCad

- jdou dělat sub-busy?

- Navrhnout Basic board

- 10x10 cm

- 9x9cm díry na M3 (Totem compatible)

- 2x32 pin bus + rezerva pro cik-cak

- data průchodka 74HC245 SMD (D0..7, R/W=dir, E&IOx=enable (?PAL))

- lišta pro výběr karty IO0..7

- PAL pro IOx, E, R, W, A0..3

- Rozhodnout mapu adres

- 32kB RAM, 8kB external, 8kB I/O (posledních 8*16 adres), 16kB ROM (paged RAM?)

- PIA MC68B21 po resetu ma A-port pull-up a B-port HighRes, to jde využít pro nastavení defaultního stránkování (aspoň ROM a ta už nastaví všechny ostatní stránky - otázka, zvládnu 2x8kB ROM namapovat, nebo potřebuju reset oštřit v horní části s vektory?)

- bezzákmitová tlačítka a přepínače

- ROM bank

- ROM R/W

- RAM/ROM at RESET

- ROM/RAM karta? (asi ano, aby se dalo bankovat a použít víc karet)

- Součástky otestovat

- PIA MC68B21

- ACIA MC68B50

- OK 74 D + 02 NOR = RS Edge

- CP1205 RST/CTR ?

- Shield 02?

- Testování chipů a desek s 0/1/Z logikou bez odporů, s LEDkama

- Univerzální Monitor - Arduino

- Program pro Mega / Totem?

- intuitivní nastavování hodnot

- krokování (změnit piny v podstatě naráz)

- makra a konstanty/proměnné

- Programovací jazyk

- Emulátor 6309

- v Linuxu

- TurboVision ?

- Arduino

- Trik s SPI RAM

- odchytávání adres karet a jasná detekce přístupu

- počítání času (a jeho zobrazování)

- vnější fronty událostí (115200 b/s ACIA, fronta vstupu, RTS/CTR)

- Debugger 6309

- disassm

- asm

- IRQ

21 Done

Click to expand/collapse

- Součástky otestovat

- OK 74 D + 02 NOR = RS Edge

- test

- druhy

- treti

Blog 2024

Blog 2024